# Using SDAccel for Host and Accelerator Code Optimizations

Presented By

Peter Frey October 2, 2018

### **SDAccel Performance Optimization Agenda**

- >SDAccel Overview

- > Host Code Optimization

- >Kernel Code Optimization

- > Topological Optimization

- >Implementation Optimization

- > Performance Profiling with SDAccel

| 8 | X | LÌ | NX. |

|---|---|----|-----|

|---|---|----|-----|

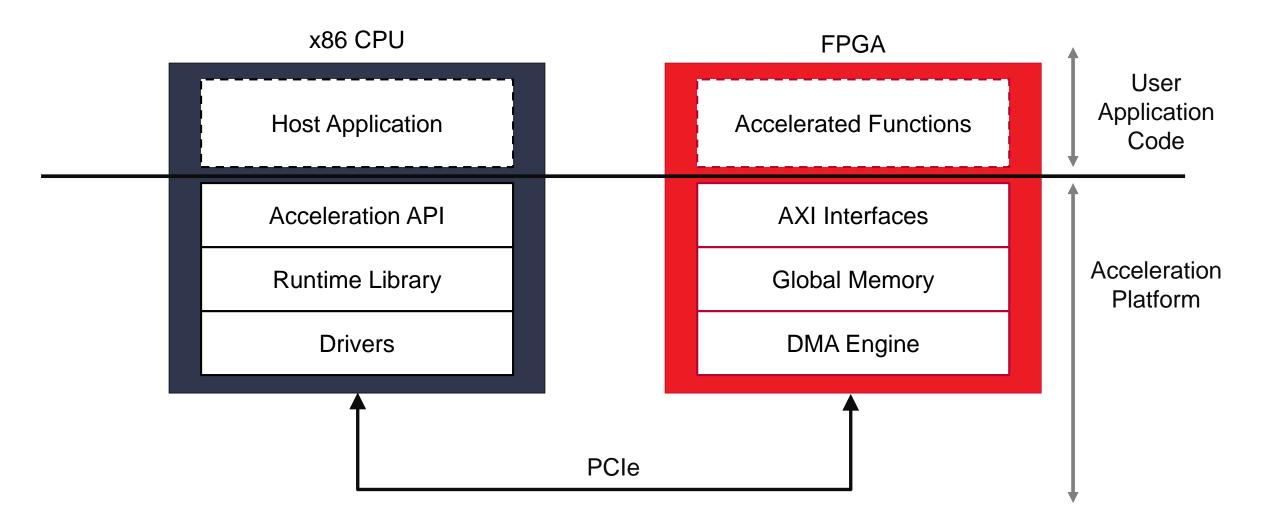

### **Architecture of an FPGA Accelerated Application**

#### **Hardware Acceleration**

#### > When to USE

- >> Algorithm allows for parallelization

- >> Many similar tasks

#### > When May Not be beneficial

- Small problem size

- Cost of Host to Device transfers outweighs benefit

Amdahl's Law: If the hardware is 50% of the time, you can accelerate the hardware to zero and you only get 2X

#### > When NOT beneficial

- Little to no parallelism

- Algorithm is highly sequential over multiple data

- Tasks are highly dependent

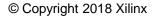

# **Overview of SDAccel**

### **Flow Overview**

**XILINX**.

© Copyright 2018 Xilinx

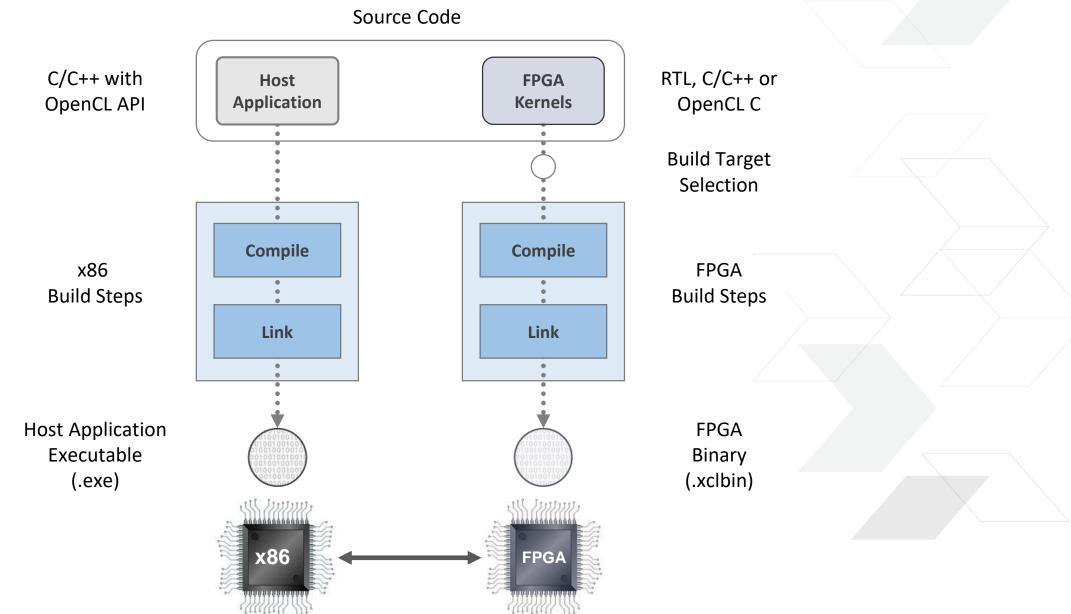

### **The FPGA Kernel Compilation Flow**

### **SDAccel Execution Modes**

| Software Emulation                                                   | Hardware Emulation                                              | Hardware Execution                                                         |

|----------------------------------------------------------------------|-----------------------------------------------------------------|----------------------------------------------------------------------------|

| Host application runs with a C/C++<br>or OpenCL model of the Kernels | Host application runs with a simulated RTL model of the Kernels | Host application runs with actual<br>FPGA implementation of the<br>Kernels |

| Confirm functional correctness of the system                         | Test the host / kernel integration, get performance estimates   | Confirm system runs correctly and with desired performance                 |

| Fastest turnaround time                                              | Best debug capabilities                                         | Accurate performance results                                               |

SSAMM

### **SDAccel Development, Debug & Analysis**

- > Designed to develop and integrate FPGA based acceleration technology into general software solutions

- > Fully integrated Eclipse based development environment

- > Automatic hardware execution flows support

- > Provides software and acceleration debugging capabilities

- > Enables detailed system performance analysis

### **Areas for Performance Optimization**

#### > Host program optimizations

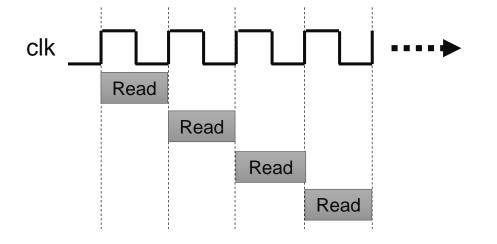

- >> Asynchronous programming, SW pipelining

- >> Optimizing transfer sizes

#### > Kernel Code optimizations-

- >> Interface Specification (512-bit, bursting interfaces)

- >> Dataflow

- >> Pipelining

- » Memory Optimization

#### > Topological optimizations

- >> Multiple CUs

- » DDR mapping

#### > Implementation optimizations

- >> SLR

- >> Other Vivado P&R controls

Vivado options provided to xocc

kernel program

coding

xocc link

options

© Copyright 2018 Xilinx

## **Host Code Optimization**

#### **Overview Host Code Optimization** Aim to reduce CPU idle time -API API func1 func3 func4 CPU WR PCle RD FPGA func2 Optimize data transfer Aim to maximize sizes kernel utilization

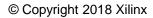

### **OpenCL Command Queue Optimization**

### **OpenCL Buffer Allocation and Transfers**

- > Buffers are used to exchange data between the host and the device

- > Aim to reuse available buffers instead of constantly allocating and deallocating new ones

- >> Reduce the overhead of DDR memory management

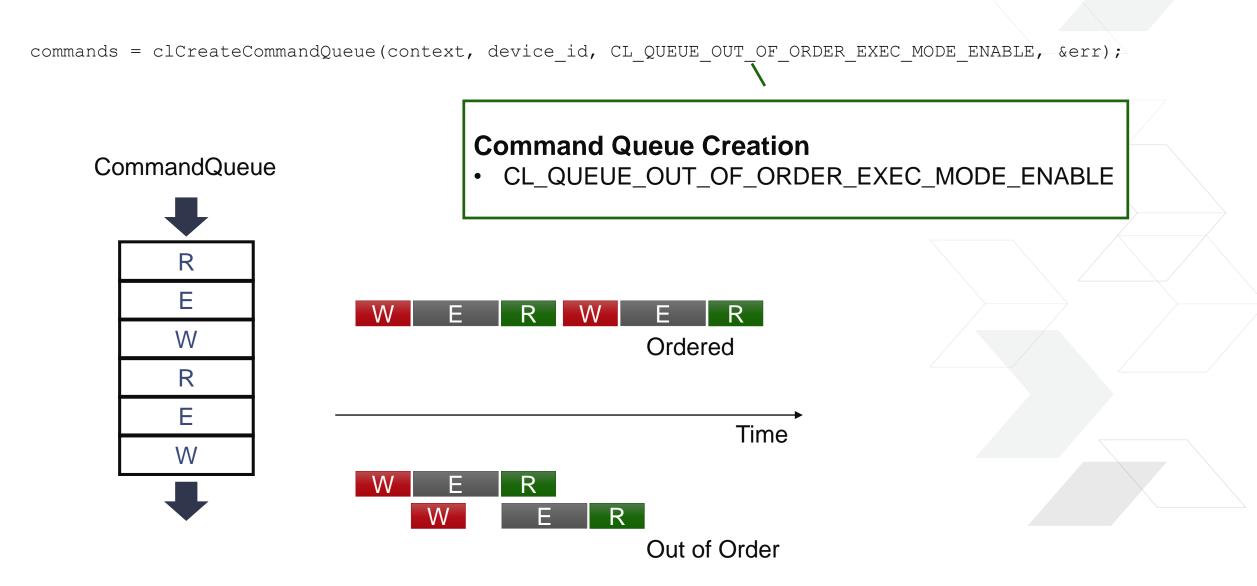

#### > Aim for 1 or 2MBytes transfers

- >> Host ⇔Device effective bandwidth varies with transfer size

- >> Allocate optimally sized buffers

- >> Group several small buffers in a single transaction

#### > READ\_WRITE buffer types can create additional dependencies impacting parallel compute unit execution

>> Only use them when necessary

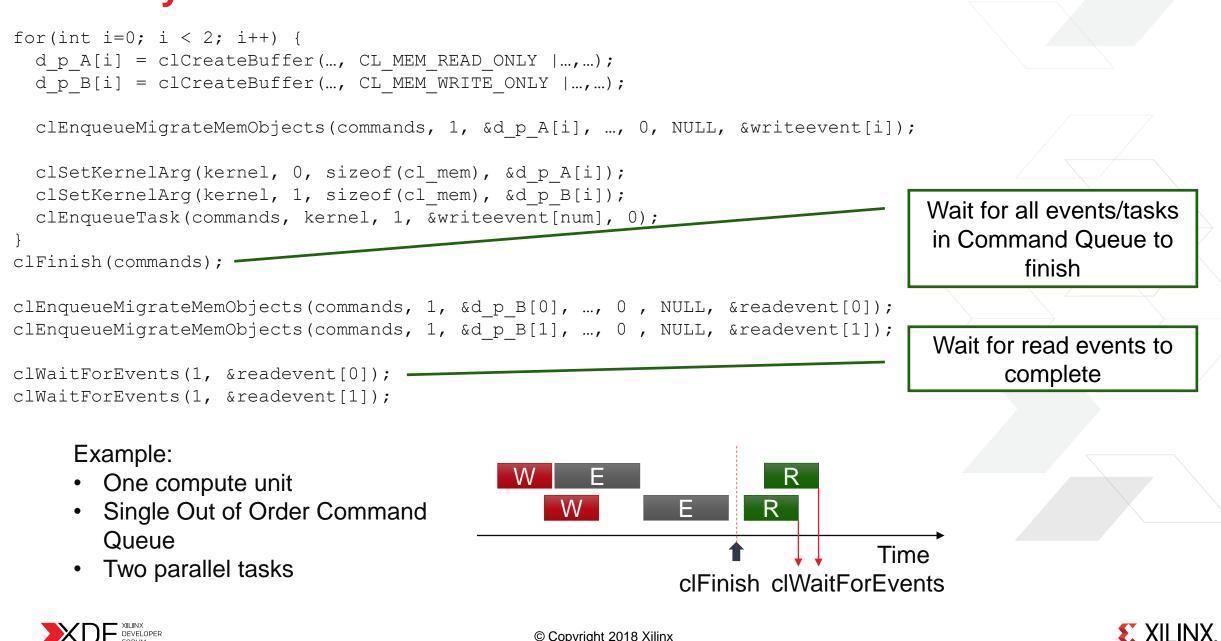

### **Task Synchronization**

© Copyright 2018 Xilinx

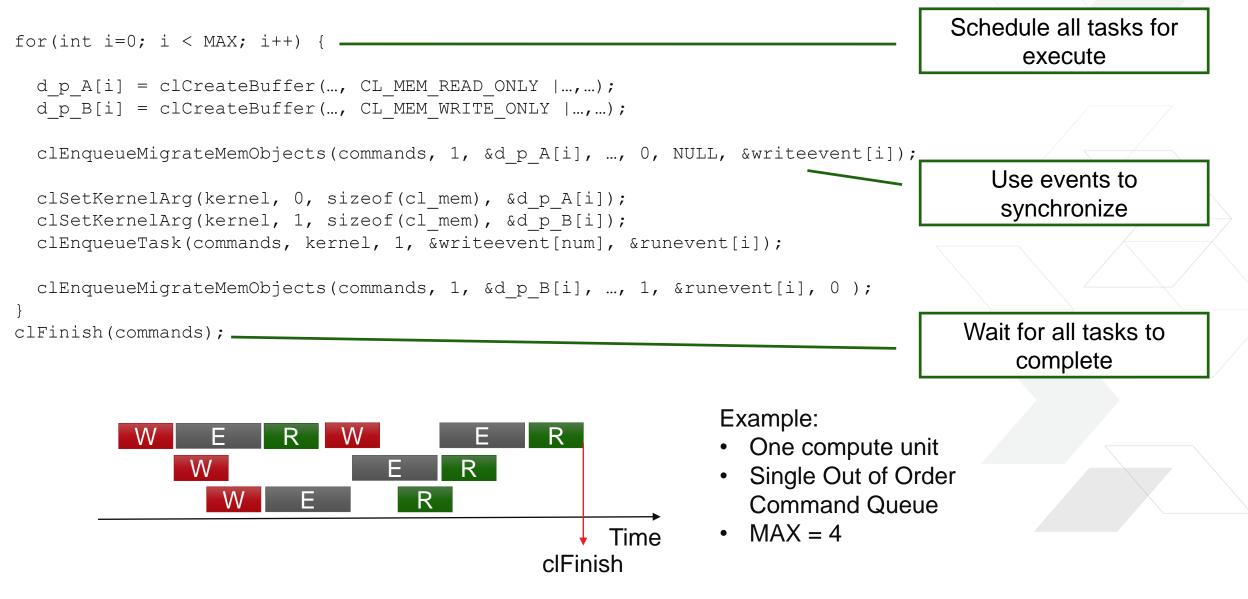

### **Software Pipelining**

# **Kernel Code Optimization**

### **Key Techniques to Develop High Performance C Kernel**

#### **1.** Improving Computation efficiency : Parallelize

- >> Customized data type adjusted to requirement

- >> Pipeline and Dataflow

- >> Unroll (Not always required)

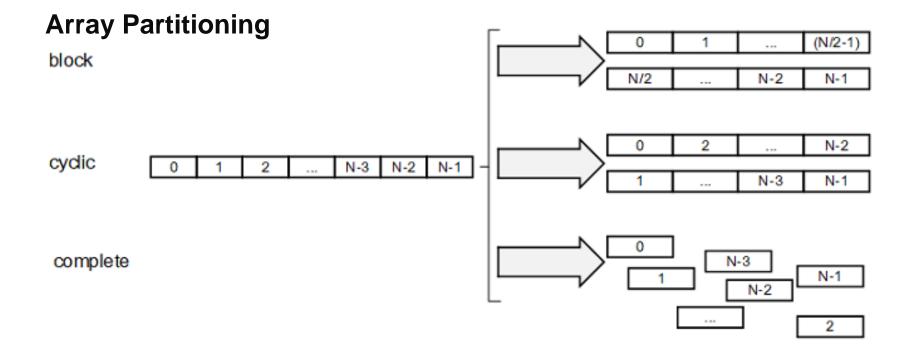

#### 2. Memory Configuration

- >> Memory customization by array partition

- >> Reduce memory access by using local caches, shift registers

#### **3.** Interface and Datatype Optimization

- >> Interface bandwidth consideration

- >> Memory Burst Read and Write

### **Datawidth Optimization: Bit Accurate Datatypes**

- > Leverage Arbitrary precision datatypes from HLS library

- >> AP\_INT, AP\_UINT

- >> AP\_FIXED, AP\_UFIXED

- > Using exact bit width helps to reduce the resource and achieve better performance

- >> Practical example: Floating point to Fixed point conversation improve performance

- >> A whitepaper: <u>Deep Learning with INT8 Optimization</u>

```

ap_uint<5> last_i; // 5 bits unsigned

ap_uint<2> tu_size ; // 2 bits unsigned

switch (tu_size) {

case 0:

last_i = 0;

break;

case 1:

last_i = 7;

break;

case 2:

last_i = 15;

break;

case 3:

last_i = 31;

break;

```

Example code shows using bit-accurate integer datatype instead of native short, int etc

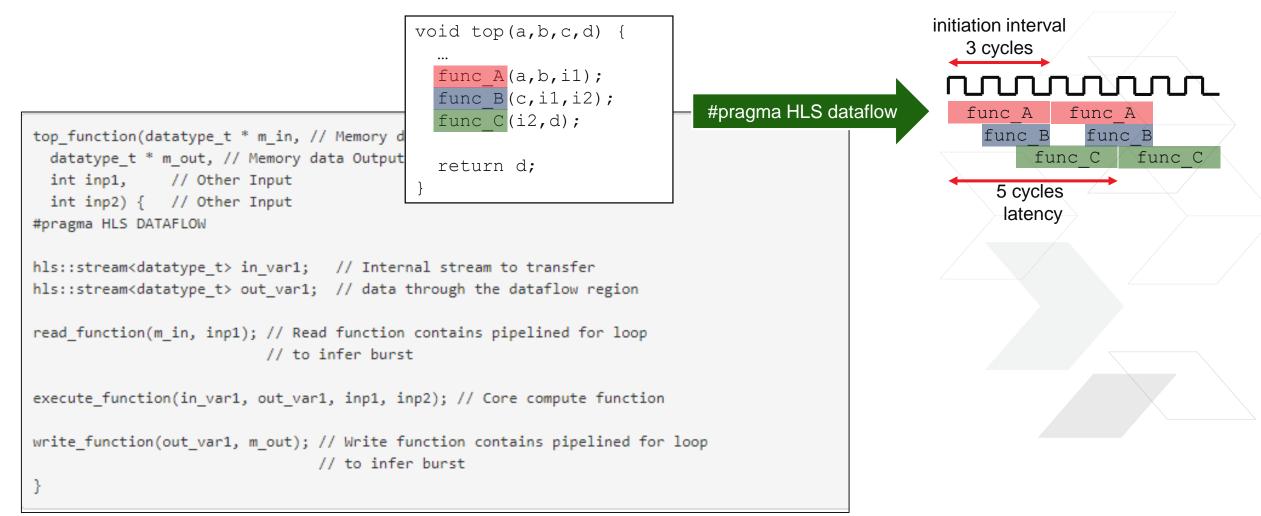

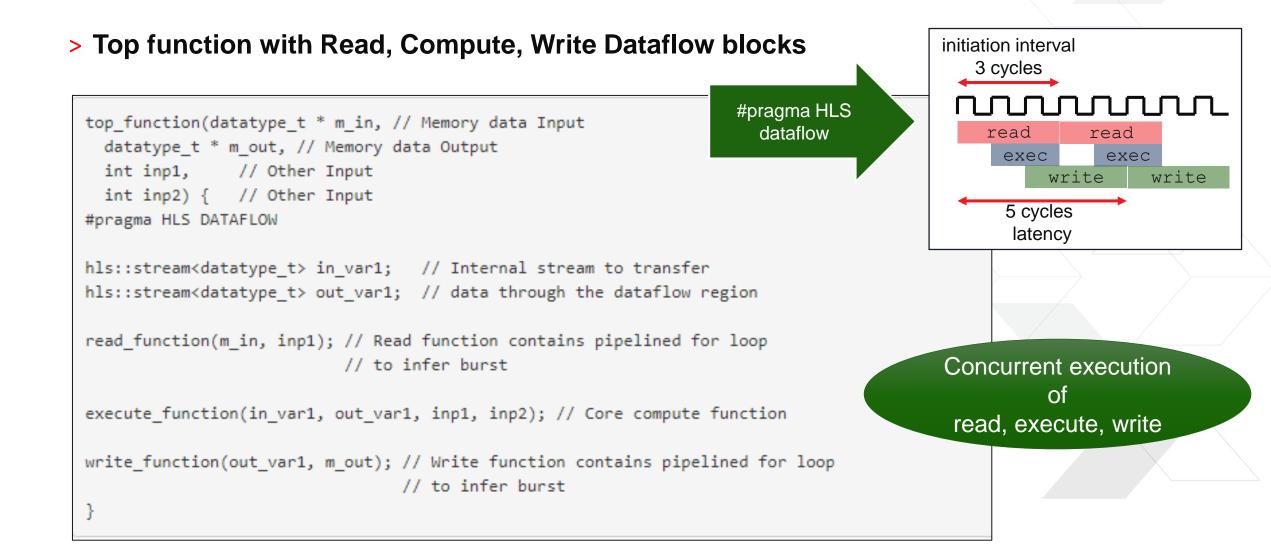

### **Improve Compute Efficiency: Dataflow**

#### > Dataflow = Task level parallelism

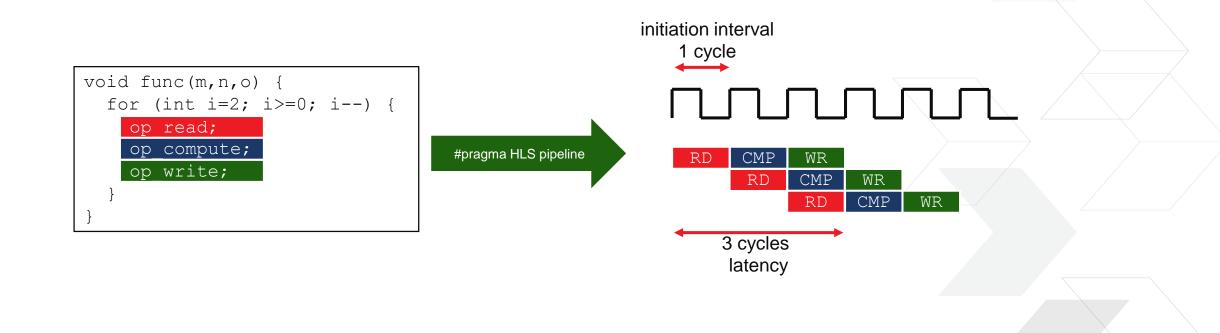

### **Improve Compute Efficiency: Pipeline**

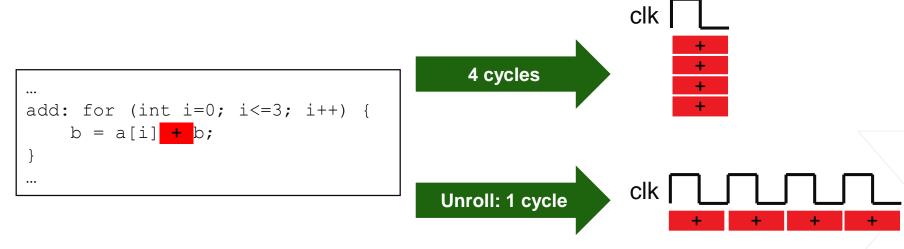

### Improve Compute Efficiency: Unrolling Loops

> For smaller body loops with limited number of iterations, unrolling improve performance

- > If complete unrolling is not feasible, exploit partial unrolling

- > Unrolling loops with large number of iterations and large body significantly increases resource usage and slows down compilation

### **Key Techniques to Develop High Performance C Kernel**

#### **1.** Improving Computation efficiency : Parallelize

- >> Customized data type adjusted to requirement

- >> Pipeline and Dataflow

- >> Unroll (Not always required)

#### 2. Memory Configuration

- >> Memory customization by array partition

- >> Reduce memory access by using local caches, shift registers

- **3.** Interface and Datatype Optimization

- >> Interface bandwidth consideration

- >> Memory Burst Read and Write

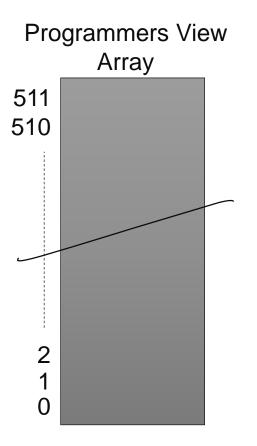

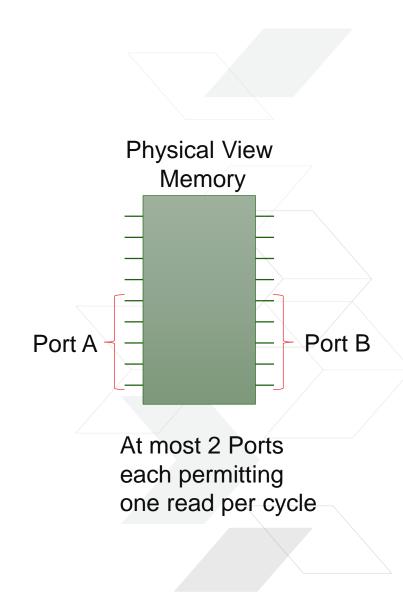

### Large Arrays get placed in Memory

```

for ( int i=0; i<512; i++) {

b = a[i] + b;

}</pre>

```

Mapping the array 'a' to a single memory will force a sequential implementation of the algorithm

### **Memory Access crucial for Performance**

- > Understand the Array access pattern

- > Use several BRAMS or Registers to implement arrays (parallel access)

© Copyright 2018 Xilinx

### **Key Techniques to Develop High Performance C Kernel**

#### **1.** Improving Computation efficiency : Parallelize

- >> Customized data type adjusted to requirement

- >> Pipeline and Dataflow

- >> Unroll (Not always required)

#### 2. Memory Configuration

- >> Memory customization by array partition

- >> Reduce memory access by using local caches, shift registers

#### **3.** Interface and Datatype Optimization

- >> Interface bandwidth consideration

- >> Memory Burst Read and Write

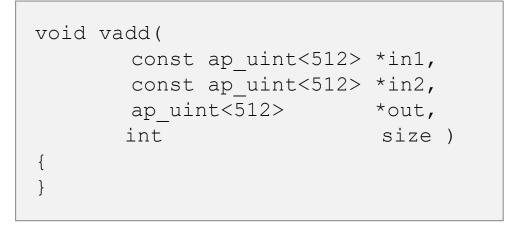

### **Interface Bandwidth Optimization – 512 bits**

> Kernels use AXI4 MM Master ports to connect with DDR banks over an AXI interconnect

- > AXI Interconnect supports up to 512 bit wide transfers

- > For maximum throughput, the kernel should use the full 512 bits of the AXI interface

Interfaces are 512bit wide

Use ap\_uint<512> types to create 512-bit wide AXI\_M ports

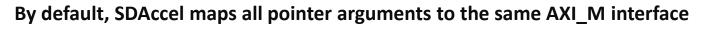

### **Interface Bandwidth Optimization – Number of Ports**

#### > Number of AXI\_M ports impacts kernel performance

>> Maximum theoretical bandwidth per AXI\_M port is 512bits @ 300MHz (based on platform clock)

#### > By default, SDAccel creates a single AXI\_M port per kernel

>> Different I/O processes will have to access the AXI\_M port sequentially

Single AXI\_M port

**EXILINX**

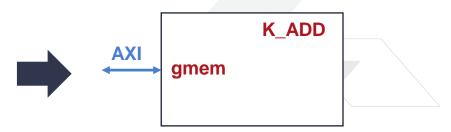

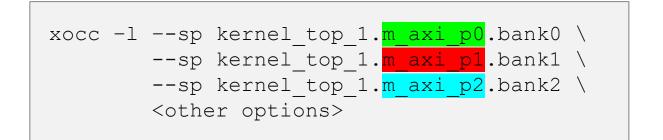

### **Interface Bandwidth Optimization – Number of Ports**

#### > Number of AXI\_M ports impacts kernel performance

>> Maximum theoretical bandwidth per AXI\_M port is 512bits @ 300MHz (based on platform clock)

#### > By default, SDAccel creates a single AXI\_M port per kernel

>> Different I/O processes will have to access the AXI\_M port sequentially

#### > Adding extra AXI\_M ports increases kernel bandwidth

>> With at least two ports, a kernel can read inputs and write outputs simultaneously

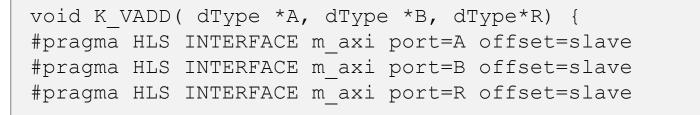

| void K_VADD( dType *A, dType *B, dType*R) { |     |           |       |        |              |                         |

|---------------------------------------------|-----|-----------|-------|--------|--------------|-------------------------|

| #pragma                                     | HLS | INTERFACE | m_axi | port=A | offset=slave | bundle= <mark>p0</mark> |

| #pragma                                     | HLS | INTERFACE | m_axi | port=B | offset=slave | bundle= <mark>p1</mark> |

| #pragma                                     | HLS | INTERFACE | m_axi | port=R | offset=slave | bundle= <mark>p2</mark> |

Use the "bundle" property on the INTERFACE pragma to create and name AXI\_M ports

#### Multiple AXI\_Master ports

### **Interface Bandwidth Optimization – Bursting**

- > Read/Write accesses to DDR cause have a long latency overhead

- > Random sequences of individual accesses are bad for performance

- > Bursting is the most efficient way to access DDR as it hides latency

- > To ensure bursting behavior, create a dedicated dataflow function in which a pipelined loop reads or writes from an AXI\_M port

```

template<typename out_t>

void read_blocks(const out_t *in, hls::stream<out_t> &out, unsigned int blocks) {

for(unsigned int i = 0; i < blocks*2; i++) {

#pragma HLS loop_tripcount min=2048 max=2048

#pragma HLS PIPELINE

out.write(in[i]);

}

}

Sequential data access

enables streaming data

between blocks</pre>

```

### **Sustaining Interface Throughput in the Kernel**

# **Topological Optimizations**

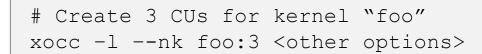

### **Multiple Compute Units (Kernel Instances)**

> By default, SDAccel generates 1 instance of each kernel

> Use multiple instances when the same function is performed on independent blocks of data (data-level parallelism)

#### > Example: 2D Image Filter

- >> Use 1 CU to process Y, U and V color planes sequentially

- >> Use 3 CUs to process Y, U and V color planes parallel

- >> Use 6 CUs to process two images in parallel

Use the xocc --nk option during the link phase to specify number of CUs for each kernel

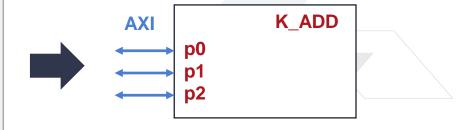

### **Kernel Port Connections to DDR Banks**

> SDAccel platforms typically contain 4 DDR banks

> By default all kernel AXI\_M ports are mapped to the same DDR bank

>> DDR bandwidth is shared, multiple AXI requests are arbitrated

#### > Careful mapping of kernel ports to specific DDR banks improves performance

User Programmable Region

p0 K\_VADD

**b**1

**p2**

AXI

AXI

AXI

- >> Take advantage of full DDR bandwidth

- >> Simultaneous transfers to each DDR

- >> Physical proximity of kernel and DDR improves Fmax

Use the xocc --sp option during the link phase to specify desired mapping Update OpenCL Buffers properties in the host program

# **Implementation Optimization**

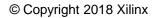

### **FPGA Physical View**

- > Today's largest FPGA are stacked silicon devices with several SLRs (super logic regions)

- > Connections between SLRs incurs a greater delay than standard intra-SLR routing

- > By default, kernels are placed in the same SLR as the Shell

- > Careful placement of kernels in SLRs will improve Fmax

- > Aim to place kernels in the same SLR as the DDR they interface with

- > Aim to minimize SLR congestion and cross-SLR connections

# **Understand the target DSA**

### > Review Documentation

- >> SDAccel Release Notes (UG 1238)

- DSA Released 2017.4

- >> DSA Specifications

### > Shell

- >> Consumes Resources to implement

- >> Removes available resources from the dyna

- >> Understand which SLRs are impacted

SLR resources and DDR assignment can impact performance

| Area                                          | SLR 0                                                                                 | SLR 1                                                                                  | SLR 2                                                                                              |  |  |

|-----------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------|--|--|

| General information                           |                                                                                       |                                                                                        |                                                                                                    |  |  |

| SLR description                               | Bottom of device; dedicated to dynamic region.                                        | Middle of device; shared by dynamic and static region resources.                       | Top of device; dedicated to dynamic region.                                                        |  |  |

| Dynamic region pblock name                    | pfm_top_i_dynamic_r<br>egion_<br>pblock_dynamic_SLR0                                  | pfm_top_i_dynamic_r<br>egion_<br>ptlock_dynamic_SLR1                                   | pfm_top_i_dynamic_r<br>egion_<br>pblock_dynamic_SLR2                                               |  |  |

| Compute unit placement<br>syntax <sup>1</sup> | <pre>set_property CONFIG.SLR_ASSIGNMENTS SLR0[get_bd_cells <cu_name>]</cu_name></pre> | <pre>se _property CC NFIG.SLR_ASSIGNMENTS SL 11 [get_bd_cells <c u_name="">]</c></pre> | <pre>set_property<br/>CONFIG.SLR_ASSIGNMENTS<br/>SLR2 [get_bd_cells<br/><cu_name>]</cu_name></pre> |  |  |

| Global memory resources availa                | able in dynamic region <sup>2</sup>                                                   |                                                                                        |                                                                                                    |  |  |

| Memory channels; system<br>port name          | bank0 (16GB DDR4)                                                                     | bank1 (16GB DDR4, in static<br>region)<br>bank2 (16GB DDR4, in<br>dynamic region)      | bank3 (16GB DDR4)                                                                                  |  |  |

| Approximate available fabric re               | sources in dynamic region                                                             |                                                                                        |                                                                                                    |  |  |

| CLB LUT                                       | 388K ( > )                                                                            | 199K — — — ( < ) — — -                                                                 | 388K                                                                                               |  |  |

| CLB Register                                  | 770К                                                                                  | зуук                                                                                   | 776К                                                                                               |  |  |

| Block RAM Tile                                |                                                                                       |                                                                                        | 720                                                                                                |  |  |

| URAM                                          |                                                                                       |                                                                                        | 320                                                                                                |  |  |

| DSP                                           | 2280                                                                                  | 1320                                                                                   | 2280                                                                                               |  |  |

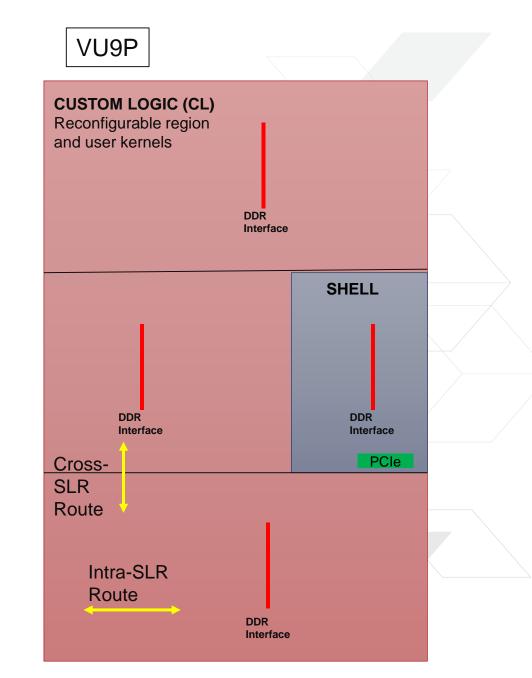

# **Kernel Placement Control**

### > Specify Kernel Locations

Provided by XOCC command line arguments

xocc <arguments> --xp param:compiler.userPostSysLinkTcl=<path>/place\_krnl.tcl

place krnl.tcl

- Auto-executes a Vivado Tcl file

- >> Kernel locations specified by Vivado Tcl script

set\_property CONFIG.SLR\_ASSIGNMENTS SLR0 [get\_bd\_cells /krnl\_0] set\_property CONFIG.SLR\_ASSIGNMENTS SLR2 [get\_bd\_cells /krnl\_1]

> Command line option provided in 2018.3

- >> Requires a new DSA revision (5.2)

- >> Also ensures local SLR reset is used

xocc <arguments> --slr krnl\_0:SLR0 --slr krnl\_1:SLR2

**E** XILINX.

# **Performance Profiling with SDAccel**

### **Main Report Files**

> SDAccel generates important report files that help to improve performance

> Reports from Hardware Emulation are most useful for performance improvement

> Guidance Report

### > Reports to analyze overall system performance (combining Host and Kernel)

- >> Profile Summary Report

- > Timeline Trace

- >> Waveform

### > Reports to understand/improve Kernel performance

- >> HLS report

- >> Schedule Viewer

**S** XILINX.

# **Design Guidance**

### > Expert system built-in the tool

- >> Analysis of build results and emulation runs

- > Guidance window with feedback by category

- >> Host code

- >> Kernels

- >> Data transfers (host to DDR, DDR to kernels)

#### > Explicit and actionable hints

- >> How to improve the design

- Links to detailed explanation and solutions

- >> HTML report (available for makefile runs as well)

| 💦 Problems 📮 Console 📄 Guidance 🛿 🔲 Properties 📗 | SDx Log   | 📃 SDx Ter | minal                                       |  |  |  |

|--------------------------------------------------|-----------|-----------|---------------------------------------------|--|--|--|

| Q   E I I Warnings ✓ ✓ 12 Met Hide All example 🗘 |           |           |                                             |  |  |  |

| Name                                             | Threshold | Actual    | Details                                     |  |  |  |

| ▼ 🔂 Emulation-HW (27)                            |           |           |                                             |  |  |  |

| 🗢 🔂 example-Default (23)                         |           |           |                                             |  |  |  |

| In Host Data Transfer (3)                        |           |           |                                             |  |  |  |

| ➡ HOST_WRITE_TRANSFER_SIZE (1)                   | > 4.096   |           |                                             |  |  |  |

| HOST_WRITE_TRANSFER_SIZE #1                      | > 4.096   | 32.768    | Host write average size was 32.768 KB a     |  |  |  |

| V THOST_MIGRATE_MEM (1)                          | > 0       |           |                                             |  |  |  |

| HOST_MIGRATE_MEM #1                              | > 0       | 8         | Migrate Memory OpenCL APIs were use         |  |  |  |

|                                                  | > 4.096   |           |                                             |  |  |  |

| HOST_READ_TRANSFER_SIZE #1                       | > 4.096   | 32.768    | Host read average size was 32.768 KB a      |  |  |  |

| マ 🔂 Resource Usage (6)                           |           |           |                                             |  |  |  |

| KERNEL_UTIL (1)                                  | = 100.000 |           |                                             |  |  |  |

| ✓ KERNEL_UTIL #1                                 | = 100.000 | 100.000   | Kernel run - global size: 1, local size: 1. |  |  |  |

| V KERNEL_COUNT (1)                               | > 1       |           |                                             |  |  |  |

| • KERNEL_COUNT #1                                | > 1       | 1         | Kernel run was executed 4 time(s) with      |  |  |  |

| ✓ OVERUSED_CUS (1)                               | < 16      |           |                                             |  |  |  |

| ✓ OVERUSED_CUS #1                                | < 16      | 1         | Kernel run required 1 compute unit call     |  |  |  |

| ▼ DEVICE_UTIL (1)                                | > 0       |           |                                             |  |  |  |

| ✓ DEVICE_UTIL #1                                 | > 0       | 0.339     | Device xilinx_kcu1500_dynamic_5_0-0         |  |  |  |

|                                                  | 50        |           |                                             |  |  |  |

|                                                  |           |           |                                             |  |  |  |

**E** XILINX

# **Profile Summary**

### > Top Operations

> Activity summary

### > Kernel & Compute Units

>> Detailed execution statistics

### > Data Transfer

- Solution Statistics From host and from kernels

- > Host Code OpenCL API statistics

| Гор                       | Operations                                     | Kernels & Com             | pute Units                    | Data Transfe | rs OpenCL.                  | APIs     |                  |                        |          |

|---------------------------|------------------------------------------------|---------------------------|-------------------------------|--------------|-----------------------------|----------|------------------|------------------------|----------|

|                           | D <mark>ata Transfer: I</mark><br>ntext:Number | Host and Glob<br>Transfer | <b>al Memory</b><br>Number Of | Transfer     | Average Ba                  | ndwidth  | Average          | Total                  | Average  |

| of [                      | Devices                                        | Type                      | Transfers                     | Rate (MB/s)  | Utilization                 |          | Size (KB)        | Time (ms)              | Time (ms |

| cor                       | ntext0:1                                       | READ                      | 128                           | N//          |                             | N/A      | 8.192            |                        |          |

| 00                        | ntext0:1                                       | WRITE                     | 252                           | N//          | A                           | N/A      | 8.192            | N/A                    |          |

| _                         |                                                |                           |                               |              | ( armal                     |          |                  |                        |          |

|                           | /ice                                           |                           | Compute Ur<br>Port Name       |              | Kernel<br>Arguments         | DDR Bank | Transfer<br>Type | Number Of<br>Transfers |          |

| ∨ <b>D</b><br>Dev<br>xili | vice<br>inx_kcu1500_d                          | ynamic_5_0-0              | Port Name                     | , A          | Kernel<br>Arguments<br>in_r | DDR Bank | Type<br>0 READ   | Transfers<br>163       | Rate (   |

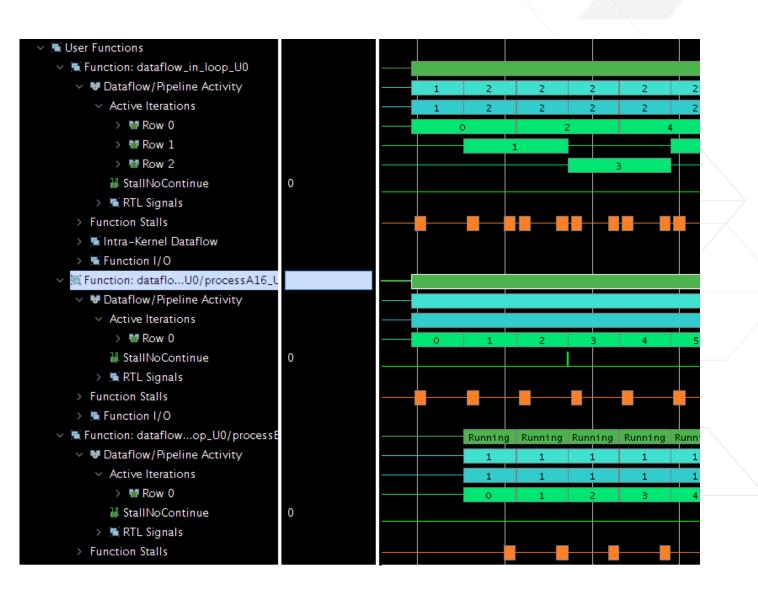

### **Annotated Waveform Viewer**

- > Shows task-level parallelism in action

- Show how many tasks overlap and for how long

# **HLS Report**

### > Static Performance Estimates:

- >> Timing

- >> Latency

- >> Hierarchical contribution

### > Utilization Estimates:

- >> Summary

- >> Detail analysis

### Performance Estimates

#### Timing (ns)

#### Summary

| Clock  | Target | Estimated | Uncertainty |

|--------|--------|-----------|-------------|

| ap_clk | 5.00   | 3.123     | 0.62        |

#### Latency (clock cycles)

#### Summary

|   | Latency |     | Inte    |     |      |

|---|---------|-----|---------|-----|------|

| 1 | min     | max | min max |     | Туре |

| 1 | 257     | 257 | 257     | 257 | none |

Detail

🗉 Instance

🗉 Loop

#### **Utilization Estimates**

#### Summary

| Name                | BRAM_18K | DSP48E | FF      | LUT    |

|---------------------|----------|--------|---------|--------|

| DSP                 | -        | -      | -       | -      |

| Expression          | -        | -      | 0       | 53     |

| FIFO                | -        | -      | -       | -      |

| Instance            | -        | -      | 0       | 1362   |

| Memory              | -        | -      | -       | -      |

| Multiplexer         | -        | -      | -       | 1173   |

| Register            | -        | -      | 47      | -      |

| Total               | 0        | 0      | 47      | 2588   |

| Available           | 4320     | 5520   | 1326720 | 663360 |

| Available SLR       | 2160     | 2760   | 663360  | 331680 |

| Utilization (%)     | 0        | 0      | ~0      | ~0     |

| Utilization SLR (%) | 0        | 0      | ~0      | ~0     |

| + 2019 Vilipy       |          |        |         |        |

**E** XILINX.

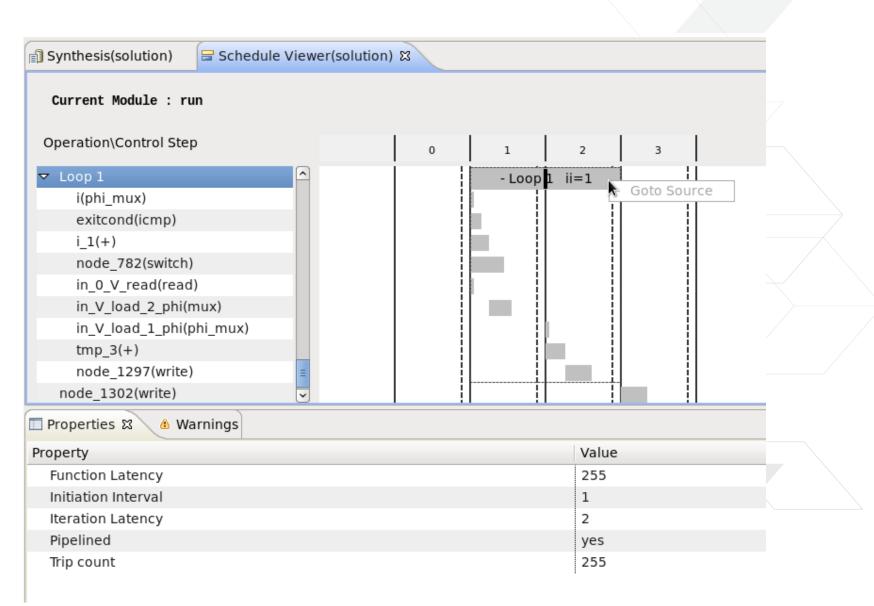

# **HLS Schedule Viewer**

- Shows in which cycle operations are scheduled

- Shows operator timing and clock margin

- > Shows data dependencies

- > Cross-probing from operations to source code

- > Supports specific focus on:

- >> II Violation

- >> Timing Violation

> First address Guidance Suggestions provided by SDAccel

> Use performance analysis viewers to identify further optimization opportunities

#### > Consider all areas for Performance Optimization

- >> Host program optimizations

- >> Kernel Code optimizations

- >> Topological optimizations

- >> Implementation optimizations

> UG1207: SDAccel Environment Optimization Guide

> SDAccel Examples:

https://github.com/Xilinx/SDAccel\_Examples

### XILINX DEVELOPER FORUM

© Copyright 2018 Xilinx