# **OVS OFFLOAD**

# Xilinx Alveo powers OVS OFFLOAD

### INTRODUCTION

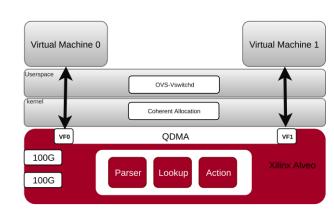

Open vSwitch (OVS) Offload application implemented on Xilinx® Alveo™ Data Center Accelerator cards allows virtual) machines (VMs to communicate with each other in the external world.

The OVS software based solutions are not only CPU intensive which affects the system performance but also prevents full utilization of the available bandwidth. By offloading the full packet processing functionality to the Xilinx Alveo platform, users can save CPU core and improve packet processing performance.

#### **KEY BENEFITS**

- Line rate throughput up to 100G

- · Kernel flow table offload

- P4 Based parsing (a context for Match-Action definitions)

- SR-IOV with DPDK Drivers (no additional drivers required)

- · Offers ideal platform for acceleration of NFV based networks

- Openflow controller support

- Fastpath forwarding of traffic between specified vSwitch vPorts

## **SOLUTION BRIEF**

- Offloads the OVS data plane to FPGA

- Improve OVS performance by 4x

- Save CPU by offloading the tasks

- · Carrier SDN and NFV appliances

- Approximately 35-40% FPGA Utilization on Alveo U200

### **SOLUTION OVERVIEW**

OVS Offload is a 100/50/25G solution which improves performance and efficiency by offloading the switching activities to the Xilinx Alveo platform.

- Offload OVS data path

- · Acceleration via Exact Match Flow Cache

- OVSDB (configuration)

- Open Flow protocol support

- TC-Flower support

- Optional Local Flow API

- VXLAN Tunnel Support

- · Stand-alone or controller modes

- Data Throughput is addressed by

- SRIOV-QDMA from Xilinx for VM data transfer

- 100G CMAC for External data traffic

# OVS OFFLOAD

# Xilinx Alveo powers OVS OFFLOAD

#### **SOLUTION DETAILS**

- Support for 252 Virtual and 4 physical functions

- Low resource utilization on the U200 allows the implementation of other acceleration functions

- Flexibility with number of table entries for Flow Tables

- SDNet /P4 design flow for packet processing

- ODL carbon support

- 32K exact match table

- Poll mode driver support for DPDK

- 1K Bit length key and action field support

- VXLAN Tunneling support

- OVS statistics support

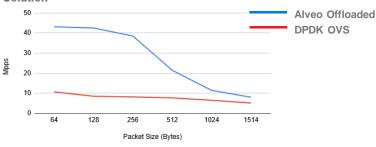

#### RESULTS

OVS Performance data and CPU Utilization as per packet size

# Comparision of DPDK OVS v/s Alveo Offload Solution

| Packet Size | With Alveo OVS Offload |                     | With DPDK OVS |                        |

|-------------|------------------------|---------------------|---------------|------------------------|

|             | Mpps                   | CPU Utilization (%) | Mpps          | CPU Utilization<br>(%) |

| 64          | 43.1                   | 15.1                | 10.64         | 65                     |

| 128         | 42.5                   | 15.2                | 8.49          | 65.1                   |

| 256         | 38.51                  | 15.2                | 8.14          | 65                     |

| 512         | 21.41                  | 15.2                | 7.66          | 65.1                   |

| 1024        | 11.4                   | 15.2                | 6.47          | 65                     |

| 1514        | 7.99                   | 15.2                | 5.1           | 65.1                   |

### TAKE THE NEXT STEP

Learn more about Xilinx: <u>Alveo accelerator cards</u> Learn more about Partner: <u>https://www.vvdntech.com/</u>

Reach out to VVDN sales:

Vinod Soman: <a href="mailto:vinod.soman@vvdntech.com">vinod.soman@vvdntech.com</a> (US Sales) Nitin Jain: <a href="mailto:nitin.jain@vvdntech.com">nitin.jain@vvdntech.com</a> (India Sales)